# Self-Assembled Incorporation of Modulated Block Copolymer Nanostructures in Phase-Change Memory for Switching Power Reduction

Woon Ik Park,<sup>†,||</sup> Byoung Kuk You,<sup>†,||</sup> Beom Ho Mun,<sup>†</sup> Hyeon Kook Seo,<sup>†,‡</sup> Jeong Yong Lee,<sup>†,‡</sup> Sumio Hosaka,<sup>§</sup> You Yin,<sup>§</sup> C. A. Ross,<sup>⊥</sup> Keon Jae Lee,<sup>†,\*</sup> and Yeon Sik Jung<sup>†,\*</sup>

<sup>†</sup>Department of Materials Science and Engineering, Korea Advanced Institute of Science and Technology (KAIST), 291 Daehak-ro, Yuseong-gu, Daejeon 305-701, Republic of Korea, <sup>‡</sup>Center for Nano Materials and Chemical Reactions, IBS, 291 Daehak-ro, Yuseong-gu, Daejeon 305-701, Republic of Korea, <sup>§</sup>Graduate School of Engineering, Gunma University, 1-5-1 Tenjin, Kiryu, Gunma 376-8515, Japan, and <sup>⊥</sup>Department of Materials Science and Engineering, Massachusetts Institute of Technology, 77 Massachusetts Avenue, Cambridge, Massachusetts 02139, United States. <sup>II</sup>W.I.P. and B.K.Y. contributed equally to this work.

**ABSTRACT** Phase change memory (PCM), which exploits the phase change behavior of chalcogenide materials, affords tremendous advantages over conventional solid-state memory due to its nonvolatility, high speed, and scalability. However, high power consumption of PCM poses a critical challenge and has been the most significant obstacle to its widespread commercialization. Here, we present a novel approach based on the self-assembly of a block copolymer (BCP) to form a thin

nanostructured SiO<sub>x</sub> layer that locally blocks the contact between a heater electrode and a phase change material. The writing current is decreased 5-fold (corresponding to a power reduction by 1/20) as the occupying area fraction of SiO<sub>x</sub> nanostructures is increased from a fill factor of 9.1% to 63.6%. Simulation results theoretically explain the current reduction mechanism by localized switching of BCP-blocked phase change materials.

KEYWORDS: block copolymers · self-assembly · phase change memory

hase change memory (PCM) is one of the most promising candidates for universal nonvolatile memory and a key component of portable electronic devices.<sup>1–3</sup> In order to be used as a core memory for mobile devices, its writing current should be minimized below at least one-third of its present level.<sup>1,4,5</sup> The writing current of PCM scales with the switching volume of the phase change material, and thus the power consumption per cell diminishes with a decrease of cell size. $^{6-8}$  However, the scalingdown of memory devices is becoming more challenging due to the diffraction limitation of optical lithography.<sup>1</sup> Novel and useful approaches that are applicable independently of a given technology node should thus be sought. Although there have been many attempts to reduce the writing current, including the engineering of materials, structures (U-cup, edge contact, ring-type, etc.), and interfaces,<sup>6,9–14</sup> sufficient power reduction has not been achieved.

Block copolymer (BCP) self-assembly, which is driven by the microphase separation of two mutually incompatible blocks, can create ordered arrays of sub-20 nm features.<sup>15-24</sup> BCP self-assembly is now considered to be a viable route to sub-16 nm lithography nodes due to its excellent resolution, scalability, and compatibility with the conventional CMOS process.<sup>1,20,21,23-29</sup> We have previously reported the large-area fabrication of oxide and metallic nanostructures such as wires, dots, and rings with an exceptional degree of long-range ordering and tunability using Si-containing BCPs.<sup>18-20,32,33</sup> Although previous studies demonstrated the memory characteristics of various nanostructures prepared from BCP nanotemplates without using high-cost nanolithography,<sup>34–38</sup> the key distinction of this study is that the dramatic performance enhancement of near-commercialized nonvolatile memory devices is achieved using the self-assembly technology. We show how a bottom-up

\* Address correspondence to ysjung@kaist.ac.kr; keonlee@kaist.ac.kr.

Received for review January 2, 2013 and accepted March 1, 2013.

Published online March 01, 2013 10.1021/nn4000176

© 2013 American Chemical Society

VOL. 7 • NO. 3 • 2651-2658 • 2013

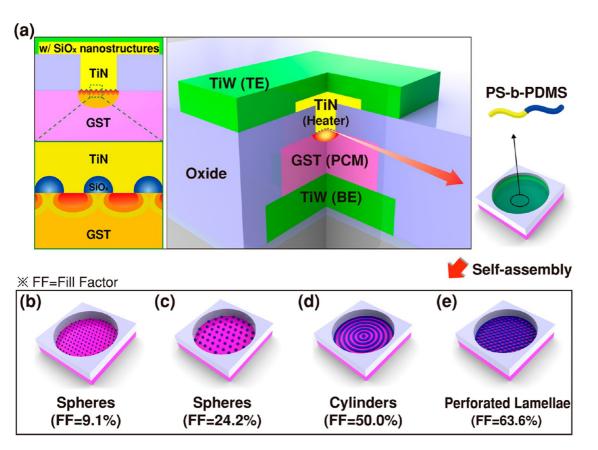

Figure 1. PCM devices and current-blocking SiO<sub>x</sub> nanostructures. The morphologies and fill factors (FF) of the nanostructures were controlled using the self-assembly of Si-containing PS-*b*-PDMS block copolymers. (a) Schematic of the PCM device structure. (b–e) Different morphologies of the self-assembled nanostructures between GST and TiN. (b) Small spheres (FF = 9.1%), (c) large spheres (24.2%), (d) cylinders (50.0%), and (e) hexagonally perforated lamellae (HPL) (63.6%).

approach can resolve the chronic issue of power consumption in phase change memory independently of shrinking the memory cell size.

In this study, the interface between the phase change material and the heater electrode is engineered by incorporating insulating silica nanostructures. Our simulation results suggest that the switching volume of the phase change material can be reduced without requiring expensive advanced nanolithography. The reset current of PCM devices decreases in proportion to the reduction of the contact area between a phase change Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) thin film and a TiN resistive heater.<sup>39</sup> Contact between GST and TiN is made only in the open region (e.g., hole) without the SiO<sub>x</sub> nanostructures. In order to control the contact area effectively, we employed the self-assembly of Sicontaining poly(styrene-b-dimethylsiloxane) (PS-b-PDMS) BCPs, whose fill factor and pattern geometry could be tailored over a wide range at the interface between a GST and a TiN (Figure 1a). The self-assembled PDMS microdomains can easily be converted into thermally stable and insulating SiO<sub>x</sub> nanostructures after a short reactive ion etch (RIE) with an  $O_2$  plasma.<sup>15,17,18,40</sup> Alternatively, various additional insulating oxide nanostructures can be formed by other pattern transfer techniques such as sequential infiltration synthesis (SIS).<sup>41</sup> Furthermore, the geometries and area fill factors of the SiO<sub>x</sub> nanostructures can be easily controlled by changing the molecular weight (MW) of BCPs and the parameters of solvent vapor annealing.<sup>18,22</sup> Thus, as schematically shown in Figure 1b–e, various SiO<sub>x</sub> nanostructures with tailored geometries and area filling factors were generated on GST thin films, enabling the effective control of temperature distributions in a PCM device.

## **RESULTS AND DISCUSSION**

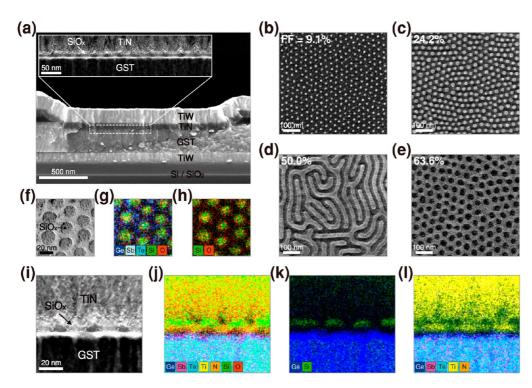

First, we demonstrate how the geometries and fill factors of blocking oxide nanostructures on GST thin films can be controlled. Fill factor is defined as the occupying area fraction of SiO<sub>x</sub> nanostructures on GST film, and the contact area between GST and TiN is decreased by increasing the fill factor. Scanning electron microscopy (SEM) images of self-assembled SiO<sub>x</sub> nanostructures formed within the circular hole of a PCM device are shown in Figure 2. The long-range uniformity of the SiO<sub>x</sub> nanostructures was previously confirmed by grazing-incidence small-angle X-ray scattering (GISAXS).<sup>17</sup> The SiO<sub>x</sub> nanostructures were obtained from BCPs forming spherical (Figure 2b and c), cylindrical (Figure 2d), and hexagonally perforated lamellar (HPL) (Figure 2e) morphologies, and their fill

Figure 2. SEM and TEM analyses. (a) Cross-sectional SEM images of the PCM device. The inset shows a TEM image of the interface between TiN and GST, where the self-assembled nanostructures are incorporated. (b–e) SEM images of the self-assembled nanostructures on GST thin films. (b) Small spheres (FF = 9.1%), (c) large spheres (24.2%), (d) cylinders (50.0%), and (e) hexagonally perforated lamellae (HPL) (63.6%). (f) Top-down bright-field TEM image of the SiO<sub>x</sub> nanodots on GST. (g and h) EDS elemental mapping results of (g) Ge, Sb, Te, Si, and O and (h) Si and O. (i) Cross-sectional TEM image at the interface. (j–I) EDS elemental mapping results of (j) Ge, Sb, Te, Ti, N, Si, and O, (k) Ge and Si, and (l) Ge, Sb, Te, Ti, and N.

factors were 9.1%, 24.2%, 50.0%, and 63.6%, respectively. These four morphologies were made from three kinds of PS-b-PDMS BCPs with different MWs of 50-5, 43-8.5, and 31-14.5 kg/mol, which have PDMS volume fractions (f<sub>PDMS</sub>) of 9.8%, 17.7%, and 33.7%, respectively. Among the various morphologies, the cvlindrical and HPL nanostructures were obtained from one BCP (31–14.5 kg/mol) by changing the solvent vapor annealing conditions using mixed solvents (Figure S2). The morphology and fill factor of the selfassembled nanostructures are governed primarily by the volume fraction of the component blocks and by the MW. However, the additional control of feature size and fill factor can be obtained using a solvent-annealing method in which the film is exposed to mixtures of vapors of two preferentially segregating solvents and in which the preferential swelling of one block is achieved.<sup>18</sup> After spin-coating BCP solutions dissolved in toluene, the samples were solvent-annealed in a chamber at 25 °C for two hours. However, the selfassembly kinetics can be significantly accelerated by increasing the solvent-annealing temperature, and well-defined BCP nanostructures can be obtained even in one minute of self-assembly time, as we recently reported.42 The self-assembled polymer nanostructures were then converted into  $SiO_x$  nanostructures by plasma oxidation. These processes produced a wide range of geometries, as shown in Table 1, by affording

PARK ET AL.

TABLE 1. MW of the BCPs, Annealing Conditions, and Fill Factors for Various Self-Assembled Morphologies

| MW [kg/mol] | f <sub>PDMS</sub> [%] | annealing vapor                 | morphology | fill factor [%] |

|-------------|-----------------------|---------------------------------|------------|-----------------|

| 55          | 9.8                   | toluene                         | spheres    | 9.1             |

| 51.5        | 17.7                  | toluene                         | spheres    | 24.2            |

| 45.5        | 33.7                  | toluene                         | cylinders  | 50.0            |

| 45.5        | 33.7                  | ${\rm toluene} + {\rm heptane}$ | HPL        | 63.6            |

control over the MW and solvent-annealing parameters of the BCPs.

The uniform incorporation of the self-assembled oxide nanostructures between the GST and TiN layers without significant variation of the geometry and size was confirmed through transmission electron microscopy (TEM) analyses. Top-view TEM (Figure 2f) and energy dispersive spectroscopy (EDS) elemental mapping images (Figure 2g and h) present well-defined SiO<sub>x</sub> nanodots on a GST thin film. A cross-sectional bright-field TEM image shows SiO<sub>x</sub> nanodots between GST and TiN (Figure 2i), and EDS elemental mapping analysis results in Figure 2j, k, and I show the successful formation of silica nanostructures between the phasechanging active material and the heater electrode. The self-assembled current-blocking nanostructures locally reduce the contact area and lead to significant power reduction by decreasing the area over which current flows.

VOL.7 • NO.3 • 2651-2658 • 2013

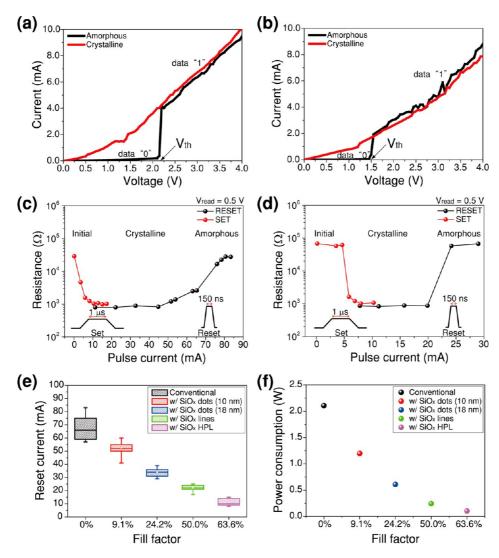

Figure 3. Electrical measurement results of the PCM devices with/without self-assembled SiO<sub>x</sub> nanostructures. (a) I–V and (c)  $R^{-1}$  curves of the PCM device without nanostructures (conventional cell). (b) I-V and (d) R-I curves of a cell with SiO<sub>x</sub> nanostructures (FF = 50%). (e) Reset current versus fill factor, showing a proportional decrease of switching current with an increase of fill factor. (f) Switching power versus fill factor. The pulse widths for SET and RESET operations were set to be 1  $\mu$ s and 150 ns, respectively.

To investigate the performance improvement of a phase-change memory by incorporation of selfassembled SiO<sub>x</sub> nanostructures, electrical tests were performed using a semiconductor parameter analyzer and a pulse generator. The procedure for fabricating PCM devices is schematically illustrated in Figure S1 in the Supporting Information. Voltage pulses were applied to the bottom electrode (TiW), while the top electrode (TiW) was grounded. For the conventional device without any self-assembled nanostructures, current-voltage (I-V) and resistance-current (R-I)curves indicate that the threshold switching, RESET, and SET voltages were 2.2, 27, and 5 V, respectively, and its reset current was estimated to be 75 mA (Figure 3a and c). On the other hand, for the device with silica nanostructures with an area fill factor of 50.0%, the threshold switching, RESET, and SET voltages were decreased to 1.5, 10, and 3 V, respectively, and the reset current

was reduced to 24 mA (Figure 3b and d). By locating SiO<sub>x</sub> nanostructures at the interface, the direct contact area between GST and TiN decreased significantly, resulting in a reduction of the threshold switching voltage and reset current (less than one-third of the reset current for the conventional cell). In addition, further work was conducted to confirm the effectiveness of this technology for a submicrometer PCM device with a contact area of 500  $\times$  500 nm<sup>2</sup>. The reset current was reduced 4-fold for the device with a fill factor of 63.6%. These results indicate that our approach of power reduction based on BCP self-assembly is applicable independently of device feature size and technology node. As we previously reported, the self-assembled SiO<sub>x</sub> nanostructures can be formed in circular trenches with a sub-50 nm diameter,<sup>19</sup> and it is therefore expected that the power-reduction mechanism can be implemented for the current state-of-the-art PCM technology.

VOL.7 • NO.3 • 2651-2658 • 2013

JAI

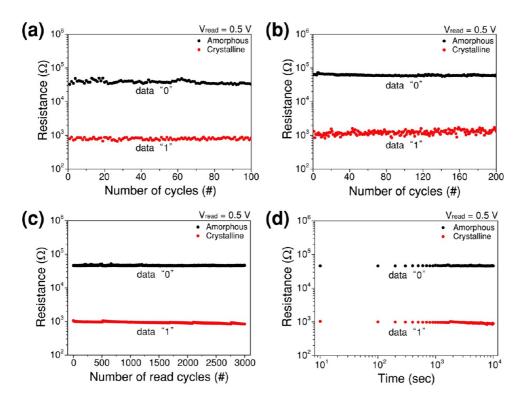

Figure 4. Device reliability evaluations. Write endurance of the PCM device (a) without and (b) with SiO<sub>x</sub> nanostructures (FF = 50%). (c) Read endurance and (d) retention time results of the PCM cells with SiO, nanostructures (FF = 50%).

The resistance ratios between the amorphous (RESET) and crystalline (SET) states remained constant regardless of fill factors. In order to observe the dependence of the reset current and the performance distribution on the contact area, PCM devices with different fill factors were measured. Figure 3e presents the cell-to-cell variations of PCM devices and the trends of the reset current with different fill factors. The small device-to-device variation in the reset current for the BCP-modified PCM devices can be attributed to the good and reproducible uniformity of the self-assembled nanostructures. The switching power per cell required for reset operation is proportional to the reset current  $(I_r)$  and cell resistance  $(R_c)$ :  $P \propto I_r^2 R_c$ .<sup>12</sup> Therefore, the power consumption required to amorphize the crystalline GST also decreases from 2.1 W to 0.10 W (approximately 20-fold power reduction) with an increasing fill factor (Figure 3f). As a result, the switching power shows an empirical dependence on the fill factor, delineated as  $P \approx (1 - FF)^{2.84}$  (Figure S5).

The endurance and retention properties of PCM devices with self-assembled nanostructures were evaluated to identify whether this approach can maintain the reliability of PCM devices, showing an on/off resistance ratio of up to  $\sim 10^2$ , which is comparable to previous studies.<sup>9,11,39</sup> PCM cells containing selfassembled SiO<sub>x</sub> nanowires with a fill factor of 50.0% exhibited good stability upon repeated switching, showing at least 200 write cycles by repetitive RESET/ SET operations at a read voltage of 0.5 V (Figure 4b). During the 200 cycles, the two states maintained

their resistance values without significant degradation, similarly to the device without the silica nanostructures (Figure 4a). Furthermore, the read endurance test results show excellent stability of around  $3 \times 10^3$  read cycles at a read voltage of 0.5 V (Figure 4c). It also showed stable retention of up to 10<sup>4</sup> s at room temperature (Figure 4d).

In order to investigate the mechanism of the enhanced behavior, the PCM devices were simulated using the electrothermal method, in which two coupled equations were solved by finite element analysis to know the heat generated by Joule heating and the temperature distribution caused by heat transfer in the device.<sup>43</sup> The mathematical model for heat transfer by conduction is heat equation

$$\rho C \frac{\partial T}{\partial t} - \nabla (k \nabla T) = Q \qquad (1)$$

where  $\rho$  is the density, T is the temperature, C is the heat capacity, k is the thermal conductivity, t is the time, and Q is the heat flux.<sup>44</sup> The heat generated by Joule heating Q is given by

$$Q = \frac{1}{\sigma} \left| J \right|^2 = \sigma \left| \nabla V \right|^2 \tag{2}$$

where  $\sigma$  is the electric conductivity, J is the electric current density, and V is the electric potential. For the simulations, we calculated the temperature profile in the GST from the switching current values obtained from measurements of the PCM devices. The existence of the self-assembled nanostructures resulted in

VOL.7 • NO.3 • 2651-2658 • 2013

JAI

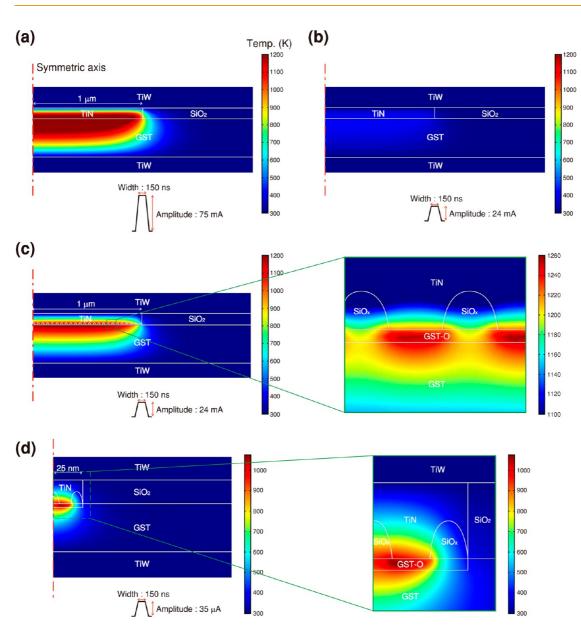

Figure 5. Temperature distributions in PCM cells calculated by electrothermal simulations. The contact hole sizes were fixed at 2  $\mu$ m except in the case of (d). (a and b) Without SiO<sub>x</sub> nanostructures. Current pulses of (a) 75 mA and (b) 24 mA. (c) With the SiO<sub>x</sub> nanostructures (FF = 50%) and an applied current pulse of 24 mA. (d) For the device with SiO<sub>x</sub> nanostructures with a much smaller cell size (contact hole diameter = 50 nm).

significantly modified temperature distributions in the GST film. For the cell without the silica nanostructures, when a reset current pulse of 75 mA (the minimum switching current measured for the conventional cell) was applied with a duration of 150 ns, the maximum temperature of the GST film was calculated to be 1330 K (Figure 5a), which is above the melting point ( $T^{melt} = 888$  K) of GST.<sup>45</sup> A lower reset current of 24 mA failed to increase the temperature over 404 K, as shown in Figure 5b, and thus reset switching was impossible at this lower current. In contrast, for the PCM structure containing the SiO<sub>x</sub> nanostructures (FF = 50%), the low current (24 mA) resulted in a maximum temperature of 1261 K (Figure 5c), which is sufficiently higher than  $T^{melt}$  of GST for the cell to be reset. The magnified view

shown in Figure 5c presents the effective role of the current-blocking SiO<sub>x</sub> nanostructures for the modification of the temperature profiles and the reduction of switching volume in the GST film. The switching volume of the cell with the silica nanostructures calculated from the area fraction of the GST that reached  $T > T^{melt}$  (888*K*) is estimated to be about 48% of the conventional device. This suggests that the reduction of switching power by the nanostructures is a result of the reduced switching volume. These simulation results support the experimental power reduction shown in Figure 3. Furthermore, the simulation indicates that this methodology would also work for devices fabricated with much smaller design rules. Similar localized heating effects and the reduction of switching current by the nanostructures

VOL.7 • NO.3 • 2651-2658 • 2013

were reproduced well for a cell with a 50 nm wide contact hole, shown in Figure 5d and Figure S6.

## CONCLUSIONS

We introduced a novel approach that shows how the switching power of PCM devices can be effectively reduced 20-fold by incorporating one simple step based on a BCP self-assembly process. The BCPmodified memory technology was successfully implemented in the PCM device, providing substantial power

### **METHODS**

**BCP Self-Assembly.** To promote the self-assembly of BCPs, the surface of the Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> film was functionalized with a hydroxy-terminated homopolymer (PS-OH, MW = 22 kg/mol) at 150 °C for 2 h under vacuum and washed with toluene to remove unreacted polymers. Then, 1.2 wt % solutions of the BCPs dissolved in toluene were spin-cast on the brush-coated GST film. In order to form uniformly monolayered SiO<sub>x</sub> nanostructures on the GST film, the thickness of the BCP film was optimized to be 25–35 nm depending on the MW of the BCPs. The BCPs were annealed at 85 °C under pure toluene or mixed vapors of heptane and toluene. The annealed samples were treated with CF<sub>4</sub> plasma (21 s at 50 W) followed by O<sub>2</sub> plasma (25 s at 60 W) using a reactive ion etching system, resulting in various self-assembled SiO<sub>x</sub> nanostructures. During the plasma oxidation, the PS brush layer on the GST film was also completely removed.

**PCM Device Fabrication.** Si samples with 150 nm thick SiO<sub>2</sub> were used as substrates. The TiW bottom electrode (150 nm) and Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> active layer (350 nm) were formed by radio frequency (RF) sputter deposition. A SiO<sub>2</sub> insulator layer with a thickness of 100 nm was prepared by plasma-enhanced chemical vapor deposition (PECVD) at 300 °C. A 2  $\mu$ m diameter hole for the contact was lithographically patterned using a mask aligner (MDA-8000B) and RIE with C<sub>4</sub>F<sub>8</sub> gas, and the BCP self-assembly process was performed. Then, a TiN heating layer (100 nm) was deposited on the Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> films with and without the SiO<sub>x</sub> nanostructures, and a TiW top electrode (200 nm) was deposited and patterned.

**Electrical Measurements.** All the electrical measurements were performed in ambient conditions by using a Keithley 4200-SCS (dc voltage sweep), a Keithley 4225-PMU (pulse generator, waveform capture of current, voltage, and resistance), a 4225-RPM (remote amplifier/switches), and a probe station. The resistances of the devices were measured at a read voltage of 0.5 V.

**TEM Measurements.** Cross-sectional transmission electron microscopy samples were prepared by mechanical polishing, followed by ion milling with Ar ions. Bright-field TEM (BFTEM) and high-resolution TEM (HRTEM) studies were performed using a JEOL JEM-ARM200F microscope operated at 200 kV.

*Conflict of Interest:* The authors declare no competing financial interest.

Acknowledgment. This work was financially supported by the Center for Integrated Smart Sensors (CISS) as Global Frontier Project (SIRC-2011-0031852), a National Research Foundation (NRF) grant (NRF-2011-220-D00063), the Basic Science Research Program (2012R1A2A1A03010415), and the Research Center Program (CA1201) of IBS (Institute for Basic Science) funded by the Ministry of Education, Science and Technology (MEST) of Korea.

*Supporting Information Available:* Supplementary figures. This material is available free of charge *via* the Internet at http://pubs.acs.org.

### **REFERENCES AND NOTES**

Derbyshire, K. ITRS 2010: A More-than-Moore Roadmap? Solid State Technol. 2011, 54, 7. reduction, independently of cell size. These results are highly meaningful in that significant power reduction can be achieved without using high-cost lithographic tools to reduce memory cell size. The simulation results in this study and our previous report on successful BCP patterning<sup>19</sup> suggest that this approach can be applied to the state-of-the-art sub-50 nm PCM devices and may also be extendable to other nonvolatile memory devices such as resistive random access memory.<sup>46</sup>

- Wuttig, M.; Yamada, N. Phase-Change Materials for Rewriteable Data Storage. *Nat. Mater.* 2007, 6, 824–832.

- Hamann, H. F.; O'Boyle, M.; Martin, Y. C.; Rooks, M.; Wickramasinghe, K. Ultra-High-Density Phase-Change Storage and Memory. *Nat. Mater.* 2006, *5*, 383–387.

- Burr, G. W.; Kurdi, B. N.; Scott, J. C.; Lam, C. H.; Gopalakrishnan, K.; Shenoy, R. S. Overview of Candidate Device Technologies for Storage-Class Memory. *IBM J. Res. Dev.* 2008, *52*, 449–464.

- Lee, M. J.; Lee, C. B.; Lee, D.; Lee, S. R.; Chang, M.; Hur, J. H.; Kim, Y. B.; Kim, C. J.; Seo, D. H.; Seo, S.; *et al.* A Fast, High-Endurance and Scalable Non-Volatile Memory Device Made from Asymmetric Ta<sub>2</sub>O<sub>(5-x)</sub>/TaO<sub>(2-x)</sub> Bilayer Structures. *Nat. Mater.* **2011**, *10*, 625–630.

- Lee, S. H.; Jung, Y.; Agarwal, R. Highly Scalable Non-Volatile and Ultra-Low-Power Phase-Change Nanowire Memory. *Nat. Nanotechnol.* 2007, 2, 626–630.

- Pirovano, A.; Lacaita, A. L.; Pellizzer, F.; Kostylev, S. A.; Benvenuti, A.; Bez, R. Low-Field Amorphous State Resistance and Threshold Voltage Drift in Chalcogenide Materials. *IEEE T. Electron Dev.* 2004, *51*, 714–719.

- Lencer, D.; Salinga, M.; Wuttig, M. Design Rules for Phase-Change Materials in Data Storage Applications. *Adv. Mater.* 2011, *23*, 2030–2058.

- Kim, C.; Suh, D. S.; Kim, K. H. P.; Kang, Y. S.; Lee, T. Y.; Khang, Y.; Cahill, D. G. Fullerene Thermal Insulation for Phase Change Memory. *Appl. Phys. Lett.* **2008**, *92*, 013109.

- Ahn, J. K.; Park, K. W.; Jung, H. J.; Yoon, S. G. Phase-Change InSbTe Nanowires Grown *in Situ* at Low Temperature by Metal-Organic Chemical Vapor Deposition. *Nano Lett.* 2010, 10, 472–477.

- Rao, F.; Song, Z. T.; Gong, Y. F.; Liangcai, L. C.; Feng, S. L.; Chen, B. M. Programming Voltage Reduction in Phase Change Memory Cells with Tungsten Trioxide Bottom Heating Layer/Electrode. *Nanotechnology* **2008**, *19*, 445706.

- Xiong, F.; Liao, A. D.; Estrada, D.; Pop, E. Low-Power Switching of Phase-Change Materials with Carbon Nanotube Electrodes. *Science* 2011, *332*, 568–570.

- Yao, D. N.; Zhou, X. L.; Wu, L. C.; Song, Z. T.; Cheng, L. M.; Rao, F.; Liu, B.; Feng, S. L. Investigation on Nitrogen-Doped Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Material for Phase-Change Memory Application. *Solid State Electron*. **2013**, *79*, 138–141.

- Wong, H. S. P.; Raoux, S.; Kim, S.; Liang, J. L.; Reifenberg, J. P.; Rajendran, B.; Asheghi, M.; Goodson, K. E. Phase Change Memory. *P. IEEE* 2010, *98*, 2201–2227.

- Park, W. I.; Yoon, J. M.; Park, M.; Lee, J.; Kim, S. K.; Jeong, J. W.; Kim, K.; Jeong, H. Y.; Jeon, S.; No, K. S.; *et al.* Self-Assembly-Induced Formation of High-Density Silicon Oxide Memristor Nanostructures on Graphene and Metal Electrodes. *Nano Lett.* **2012**, *12*, 1235–1240.

- Liang, X.; Jung, Y. S.; Wu, S.; Ismach, A.; Olynick, D. L.; Cabrini, S.; Bokor, J. Formation of Bandgap and Subbands in Graphene Nanomeshes with Sub-10 nm Ribbon Width Fabricated *via* Nanoimprint Lithography. *Nano Lett.* **2010**, *10*, 2454–2460.

- Jung, Y. S.; Chang, J. B.; Verploegen, E.; Berggren, K. K.; Ross, C. A. A Path to Ultranarrow Patterns Using Self-Assembled Lithography. *Nano Lett.* **2010**, *10*, 1000–1005.

ARTICLE

- Jung, Y. S.; Ross, C. A. Solvent-Vapor-Induced Tunability of Self-Assembled Block Copolymer Patterns. *Adv. Mater.* 2009, 21, 2540–2545.

- Jung, Y. S.; Jung, W.; Ross, C. A. Nanofabricated Concentric Ring Structures by Templated Self-Assembly of a Diblock Copolymer. *Nano Lett.* 2008, *8*, 2975–2981.

- Bita, I.; Yang, J. K. W.; Jung, Y. S.; Ross, C. A.; Thomas, E. L.; Berggren, K. K. Graphoepitaxy of Self-Assembled Block Copolymers on Two-Dimensional Periodic Patterned Templates. *Science* **2008**, *321*, 939–943.

- Ruiz, R.; Kang, H. M.; Detcheverry, F. A.; Dobisz, E.; Kercher, D. S.; Albrecht, T. R.; de Pablo, J. J.; Nealey, P. F. Density Multiplication and Improved Lithography by Directed Block Copolymer Assembly. *Science* **2008**, *321*, 936–939.

- Jung, Y. S.; Ross, C. A. Well-Ordered Thin-Film Nanopore Arrays Formed Using a Block-Copolymer Template. *Small* 2009, 5, 1654–1659.

- Park, M.; Harrison, C.; Chaikin, P. M.; Register, R. A.; Adamson, D. H. Block Copolymer Lithography: Periodic Arrays of ~10<sup>11</sup> Holes in 1 Square Centimeter. *Science* **1997**, *276*, 1401–1404.

- Chai, J.; Wang, D.; Fan, X.; Buriak, J. M. Assembly of Aligned Linear Metallic Patterns on Silicon. *Nat. Nanotechnol.* 2007, 2, 500–506.

- Kim, S. O.; Solak, H. H.; Stoykovich, M. P.; Ferrier, N. J.; De Pablo, J. J.; Nealey, P. F. Epitaxial Self-Assembly of Block Copolymers on Lithographically Defined Nanopatterned Substrates. *Nature* 2003, 424, 411–414.

- Cheng, J. Y.; Mayes, A. M.; Ross, C. A. Nanostructure Engineering by Templated Self-Assembly of Block Copolymers. *Nat. Mater.* 2004, *3*, 823–828.

- Morkved, T. L.; Lu, M.; Urbas, A. M.; Ehrichs, E. E.; Jaeger, H. M.; Mansky, P.; Russell, T. P. Local Control of Microdomain Orientation in Diblock Copolymer Thin Films with Electric Fields. *Science* **1996**, *273*, 931–933.

- Thurn-Albrecht, T.; Schotter, J.; Kastle, C. A.; Emley, N.; Shibauchi, T.; Krusin-Elbaum, L.; Guarini, K.; Black, C. T.; Tuominen, M. T.; Russell, T. P. Ultrahigh-Density Nanowire Arrays Grown in Self-Assembled Diblock Copolymer Templates. *Science* **2000**, *290*, 2126–2129.

- Black, C. T.; Ruiz, R.; Breyta, G.; Cheng, J. Y.; Colburn, M. E.; Guarini, K. W.; Kim, H. C.; Zhang, Y. Polymer Self-Assembly in Semiconductor Microelectronics. *IBM J. Res. Dev.* 2007, *51*, 605–633.

- Park, S.; Lee, D. H.; Xu, J.; Kim, B.; Hong, S. W.; Jeong, U.; Xu, T.; Russell, T. P. Macroscopic 10-Terabit-per-Square-Inch Arrays from Block Copolymers with Lateral Order. *Science* 2009, 323, 1030–1033.

- Benchera, C.; Yi, H.; Zhoua, J.; Cai, M.; Smith, J.; Miao, L.; Montalb, O.; Blitshtein, S.; Lavia, A.; Dotan, K.; *et al.* Directed Self-Assembly Defectivity Assessment. *SPIE* **2012**, 8323.

- Yang, J. K. W.; Jung, Y. S.; Chang, J. B.; Mickiewicz, R. A.; Alexander-Katz, A.; Ross, C. A.; Berggren, K. K. Complex Self-Assembled Patterns Using Sparse Commensurate Templates with Locally Varying Motifs. *Nat. Nanotechnol.* 2010, *5*, 256–260.

- Jung, Y. S.; Lee, J. H.; Lee, J. Y.; Ross, C. A. Fabrication of Diverse Metallic Nanowire Arrays Based on Block Copolymer Self-Assembly. *Nano Lett.* **2010**, *10*, 3722–3726.

- Milliron, D. J.; Raoux, S.; Shelby, R. M.; Jordan-Sweet, J. Solution-Phase Deposition and Nanopatterning of GeSbSe Phase-Change Materials. *Nat. Mater.* 2007, *6*, 352–356.

- Wei, Q. S.; Lin, Y.; Anderson, E. R.; Briseno, A. L.; Gido, S. P.; Watkins, J. J. Additive-Driven Assembly of Block Copolymer-Nanoparticle Hybrid Materials for Solution Processable Floating Gate Memory. ACS Nano 2012, 6, 1188–1194.

- Zhang, Y.; Wong, H. S. P.; Raoux, S.; Cha, J. N.; Rettner, C. T.; Krupp, L. E.; Topuria, T.; Milliron, D. J.; Rice, P. M.; Jordan-Sweet, J. L. Phase Change Nanodot Arrays Fabricated Using a Self-Assembly Diblock Copolymer Approach. *Appl. Phys. Lett.* **2007**, *91*, 3104.

- De Rosa, C.; Auriemma, F.; Di Girolamo, R.; Pepe, G. P.; Napolitano, T.; Scaldaferri, R. Enabling Strategies in Organic Electronics Using Ordered Block Copolymer Nanostructures. *Adv. Mater.* **2010**, *22*, 5414–5419.

- Jo, A.; Joo, W.; Jin, W. H.; Nam, H.; Kim, J. K. Ultrahigh-Density Phase-Change Data Storage without the Use of Heating. *Nat. Nanotechnol.* **2009**, *4*, 727–731.

- Pirovano, A.; Lacaita, A. L.; Benvenuti, A.; Pellizzer, F.; Hudgens, S.; Bez, R. Scaling Analysis of Phase-Change Memory Technology. *IEDM* 2003, 03–699, 29.6.1–29.6.4.

- Jung, Y. S.; Ross, C. A. Orientation-Controlled Self-Assembled Nanolithography Using a Polystyrene-Polydimethylsiloxane Block Copolymer. *Nano Lett.* 2007, 7, 2046–2050.

- Peng, Q.; Tseng, Y. C.; Darling, S. B.; Elam, J. W. A Route to Nanoscopic Materials *via* Sequential Infiltration Synthesis on Block Copolymer Templates. *ACS Nano* **2011**, *5*, 4600– 4606.

- Park, W. I.; Kim, K.; Jang, H.-I.; Jeong, J. W.; Kim, J. M.; Choi, J.; Park, J. H.; Jung, Y. S. Directed Self-Assembly with Sub-100 Degrees Celsius Processing Temperature, Sub-10 Nanometer Resolution, and Sub-1 Minute Assembly Time. *Small* **2012**, *8*, 3762–3768.

- Yin, Y.; Sone, H.; Hosaka, S. Simulation of Proposed Confined-Chalcogenide Phase-Change Random Access Memory for Low Reset Current by Finite Element Modelling. *Jpn. J. Appl. Phys. Lett.* **2006**, *45*, 6177–6181.

- Incropera, F. P.; Dewitt, D. P. Fundamentals of Heat and Mass Transfer, 4th ed.; John Wiley & Sons: New York, 1996; p 886.

- Kolobov, A. V.; Fons, P.; Krbal, M.; Simpson, R. E.; Hosokawa, S.; Uruga, T.; Tanida, H.; Tominaga, J. Liquid Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> Studied by Extended X-ray Absorption. *Appl. Phys. Lett.* 2009, *95*, 1902.

- Liu, Q.; Long, S. B.; Lv, H. B.; Wang, W.; Niu, J. B.; Huo, Z. L.; Chen, J. N.; Liu, M. Controllable Growth of Nanoscale Conductive Filaments in Solid-Electrolyte-Based ReRAM by Using a Metal Nanocrystal Covered Bottom Electrode. *ACS Nano* 2010, *4*, 6162–6168.